Abstract

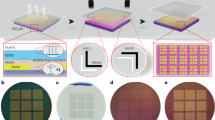

Two-dimensional semiconductors are an attractive material for making thin-film transistors due to their scalability, transferability, atomic thickness and relatively high carrier mobility. There is, however, a gap in performance between single-device demonstrations, which typically use single-crystalline two-dimensional films, and devices that can be integrated on a large scale using industrial methods. Here we report the 200-mm-wafer-scale integration of polycrystalline molybdenum disulfide (MoS2) field-effect transistors. Our processes are compatible with industry, with processing performed in a commercial 200 mm fabrication facility with a yield of over 99.9%. We find that the metal–semiconductor junction in polycrystalline MoS2 is fundamentally different from its single-crystalline counterpart, and therefore, we redesign the process flow to nearly eliminate the Schottky barrier height at the metal–MoS2 contact. The resulting MoS2 field-effect transistors exhibit mobilities of 21 cm2 V−1 s−1, contact resistances of 3.8 kΩ µm and on-current densities of 120 µA µm−1, which are similar to those achieved with single-crystalline flakes.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Data that support the findings of this study are available from the corresponding authors upon reasonable request.

Code availability

The Python code (version 3.8.5) used in this study is available from the corresponding authors upon reasonable request.

References

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Waltl, M. et al. Perspective of 2D integrated electronic circuits: scientific pipe dream or disruptive technology? Adv. Mater. 34, 2201082 (2022).

Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS2 MOSFETs. ACS Nano 6, 8563–8569 (2012).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42nm contact pitch and 250µA/µm drain current. In Proc. IEEE International Electron Devices Meeting (IEDM) 23.2.1–23.2.4 (IEEE, 2019).

Seol, M. et al. High-throughput growth of wafer-scale monolayer transition metal dichalcogenide via vertical Ostwald ripening. Adv. Mater. 32, 2003542 (2020).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Li, S. et al. Wafer-scale and deterministic patterned growth of monolayer MoS2 via vapor–liquid–solid method. Nanoscale 11, 16122–16129 (2019).

Paterson, A. F. & Anthopoulos, T. D. Enabling thin-film transistor technologies and the device metrics that matter. Nat. Commun. 9, 5264 (2018).

Chen, T.-F., Yeh, C.-F. & Lou, J.-C. Investigation of grain boundary control in the drain junction on laser-crystalized poly-Si thin film transistors. IEEE Electron Device Lett. 24, 457–459 (2003).

Billah, M. M. et al. Effect of grain boundary protrusion on electrical performance of low temperature polycrystalline silicon thin film transistors. IEEE J. Electron Devices Soc. 7, 503–511 (2019).

Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5, 5678 (2014).

Choi, M. et al. Flexible active-matrix organic light-emitting diode display enabled by MoS2 thin-film transistor. Sci. Adv. 4, eaas8721 (2018).

Meng, W. et al. Three-dimensional monolithic micro-LED display driven by atomically thin transistor matrix. Nat. Nanotechnol. 16, 1231–1236 (2021).

Hwangbo, S., Hu, L., Hoang, A. T., Choi, J. Y. & Ahn, J.-H. Wafer-scale monolithic integration of full-colour micro-LED display using MoS2 transistor. Nat. Nanotechnol. 17, 500–506 (2022).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

Xue, F. et al. Integrated memory devices based on 2D materials. Adv. Mater. 34, 2201880 (2022).

Park, H. et al. Flexible and transparent thin-film transistors based on two-dimensional materials for active-matrix display. ACS Appl. Mater. Interfaces 12, 4749–4754 (2020).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Quellmalz, A. et al. Large-area integration of two-dimensional materials and their heterostructures by wafer bonding. Nat. Commun. 12, 917 (2021).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Li, X. et al. One-dimensional semimetal contacts to two-dimensional semiconductors. Nat. Commun. 14, 111 (2023).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Jung, Y. et al. Transferred via contacts as a platform for ideal two-dimensional transistors. Nat. Electron. 2, 187–194 (2019).

Kwon, G. et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Trainer, D. J. et al. Visualization of defect induced in-gap states in monolayer MoS2. npj 2D Mater. Appl. 6, 13 (2022).

Su, J., Feng, L., Zhang, Y. & Liu, Z. Defect induced gap states in monolayer MoS2 control the Schottky barriers of Pt-mMoS2 interfaces. Appl. Phys. Lett. 110, 161604 (2017).

Velický, M. et al. Mechanism of gold-assisted exfoliation of centimeter-sized transition-metal dichalcogenide monolayers. ACS Nano 12, 10463–10472 (2018).

Huang, Y. et al. Universal mechanical exfoliation of large-area 2D crystals. Nat. Commun. 11, 2453 (2020).

Liu, F. et al. Disassembling 2D van der Waals crystals into macroscopic monolayers and reassembling into artificial lattices. Science 367, 903–906 (2020).

Nguyen, V. L. et al. Wafer-scale integration of transition metal dichalcogenide field-effect transistors using adhesion lithography. Nat. Electron. 6, 146–153 (2023).

English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Zhou, W. et al. Intrinsic structural defects in monolayer molybdenum disulfide. Nano Lett. 13, 2615–2622 (2013).

van der Zande, A. M. et al. Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide. Nat. Mater. 12, 554–561 (2013).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Kwak, I. et al. Low interface trap density in scaled bilayer gate oxides on 2D materials via nanofog low temperature atomic layer deposition. Appl. Surf. Sci. 463, 758–766 (2019).

Zhang, J. et al. Scalable growth of high-quality polycrystalline MoS2 monolayers on SiO2 with tunable grain sizes. ACS Nano 8, 6024–6030 (2014).

Najmaei, S. et al. Electrical transport properties of polycrystalline monolayer molybdenum disulfide. ACS Nano 8, 7930–7937 (2014).

Hussain, S. et al. Controlled synthesis and optical properties of polycrystalline molybdenum disulfide atomic layers grown by chemical vapor deposition. J. Alloy. Compd. 653, 369–378 (2015).

Kim, Y. et al. Wafer-scale integration of highly uniform and scalable MoS2 transistors. ACS Appl. Mater. Interfaces 9, 37146–37153 (2017).

Kim, T. et al. Wafer-scale production of highly uniform two-dimensional MoS2 by metal-organic chemical vapor deposition. Nanotechnology 28, 18LT01 (2017).

Yu, H. et al. Wafer-scale growth and transfer of highly-oriented monolayer MoS2 continuous films. ACS Nano 11, 12001–12007 (2017).

Smithe, K. K. H., Suryavanshi, S. V., Muñoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Yang, P. et al. Batch production of 6-inch uniform monolayer molybdenum disulfide catalyzed by sodium in glass. Nat. Commun. 9, 979 (2018).

Xu, H. et al. High-performance wafer-scale MoS2 transistors toward practical application. Small 14, 1803465 (2018).

Lim, Y.-F. et al. Modification of vapor phase concentrations in MoS2 growth using a NiO foam barrier. ACS Nano 12, 1339–1349 (2018).

Zhang, S. et al. Wafer-scale transferred multilayer MoS2 for high performance field effect transistors. Nanotechnology 30, 174002 (2019).

Wang, L. et al. Electronic devices and circuits based on wafer-scale polycrystalline monolayer MoS2 by chemical vapor deposition. Adv. Electron. Mater. 5, 1900393 (2019).

Mun, J. et al. High-mobility MoS2 directly grown on polymer substrate with kinetics-controlled metal–organic chemical vapor deposition. ACS Appl. Electron. Mater. 1, 608–616 (2019).

He, T. et al. Synthesis of large-area uniform MoS2 films by substrate-moving atmospheric pressure chemical vapor deposition: from monolayer to multilayer. 2D Mater. 6, 025030 (2019).

Xu, X., Wang, Z., Lopatin, S., Quevedo-Lopez, M. A. & Alshareef, H. N. Wafer scale quasi single crystalline MoS2 realized by epitaxial phase conversion. 2D Mater. 6, 015030 (2018).

Zhang, H. et al. Multilayer Si shadow mask processing of wafer-scale MoS2 devices. 2D Mater. 7, 025019 (2020).

Wang, Q. et al. Wafer-scale highly oriented monolayer MoS2 with large domain sizes. Nano Lett. 20, 7193–7199 (2020).

Durairaj, S. et al. Barrier-assisted vapor phase CVD of large-area MoS2 monolayers with high spatial homogeneity. Nanoscale Adv. 2, 4106–4116 (2020).

Yang, P. et al. Epitaxial growth of centimeter-scale single-crystal MoS2 monolayer on Au(111). ACS Nano 14, 5036–5045 (2020).

Xu, X. et al. Enhanced quality of wafer-scale MoS2 films by a capping layer annealing process. Adv. Funct. Mater. 30, 1908040 (2020).

Shinde, N. B. et al. Large-scale atomically thin monolayer 2H-MoS2 field-effect transistors. ACS Appl. Nano Mater. 3, 7371–7376 (2020).

Shi, Y. et al. Engineering wafer-scale epitaxial two-dimensional materials through sapphire template screening for advanced high-performance nanoelectronics. ACS Nano 15, 9482–9494 (2021).

Schram, T. et al. High yield and process uniformity for 300 mm integrated WS2 FETs. In 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Wang, X. et al. Pass-transistor logic circuits based on wafer-scale 2D semiconductors. Adv. Mater. 34, 2202472 (2022).

Kong, L. et al. Wafer-scale and universal van der Waals metal semiconductor contact. Nat. Commun. 14, 1014 (2023).

Zhu, J. et al. Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. Nat. Nanotechnol. 18, 456–463 (2023).

Kim, K. S. et al. Non-epitaxial single-crystal 2D material growth by geometric confinement. Nature 614, 88–94 (2023).

Acknowledgements

This work was supported by Samsung Advanced Institute of Technology, Samsung Electronics Co., Ltd.

Author information

Authors and Affiliations

Contributions

J. Kwon, M.S., K.-E.B. and J. Kim conceived the study. J. Kwon fabricated all the wafer-scale devices in this research and measured their electrical characteristics. M.S. produced the wafer-scale MoS2 films via MOCVD. J.Y. calculated the projected DOS of various types of MoS2–Au junction using DFT calculations. H.R. helped fabricate a single-crystal MoS2 FET by transferring a MoS2/hBN stack onto the bottom electrodes under the guidance of G.-H.L. D.-S.K. analysed the interfacial distances at different MoS2–Au junctions using scanning transmission electron microscopy. M.-H.L. provided a platform for the wafer-scale fabrication and electrical measurements of the MoS2 bottom-contact FETs. E.K.L. assisted with the low-temperature electrical measurements and analysis. M.S.Y. provided guidance for the experimental demonstrations of the bottom-contact FETs. H.-J.S. provided technical guidance and advice for proving this mechanism. J. Kwon, M.S., J. Kim and K.-E.B. wrote the paper. All authors contributed to the discussion.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks the anonymous reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

Extended Data Fig. 1 Benchmarking FET performances of large area TMDs.

a. Benchmark data illustrating the Ion of MoS2 FET relative to the integration scale. MoS2 growth methods were categorized as thermal CVD (brown circle), Epitaxial growth on sapphire (navy square), and MOCVD (orange triangle). Here, CVD and epitaxial growth exhibit scaling limitations, as expected, but it appears that MoS2 grown via epitaxial growth shows better performance. Although MOCVD clearly has advantages in terms of scaling, it shows limitations in performance. But this work overcomes these limitations of MOCVD and demonstrates performance as high as chip-scale research. b. Benchmark data for the Ion and channel length of large-area MoS2 classified by patterning methods. Typically, photolithography is well-suited for large-scale integration; however, it leaves a significant amount of photoresist residue and involves relatively harsh wet processes, which can be detrimental to performance. On the other hand, e-beam lithography, whereas not well-suited for integration, utilizes a relatively clean e-beam resist (ER) and is suitable for fundamental studies through small-scale components, thanks to its high resolution. In this regard, the contact region, which is most influenced by photolithography, remains unexposed in the bottom contact geometry. Therefore, bottom contact devices exhibited performance equivalent or high to those fabricated using e-beam lithography and achieved a higher on-current compared to all other devices fabricated using photolithography. All data are based on Vds = 1 V, and some values are approximately extracted, so they may not be highly precise. In cases Ion at Vds = 1 V could not be obtained, values were unavoidably extracted at the specified Vds values in each paper, indicated within parentheses.

Extended Data Fig. 2 Grain size and uniformity of MOCVD-grown 200 mm MoS2 monolayer.

a. Photograph of a MOCVD-grown MoS2 film on a 200 mm SiO2/Si wafer. b. SEM images depicting changes as the growth cycle progresses. From these SEM images, it can be observed that the average grain size ranges from 50 nm to 100 nm. The relatively darker region in the rightmost image appears to be the bilayer patch, which is estimated to have approximately 20% coverage. c. Representative Raman spectrum of the MoS2 film. A peak and E peak respectively refer to the characteristic peaks of MoS2, the A1g and E12g peaks. Additionally, a peak from silicon substrate is also observed and indicated as Si, which plays a role as a reference. By analyzing the ratio of these peaks, the quality of the film can be indirectly checked. d. Raman spectrum map of the intensity ratio of the A1g peak to the Si peak, conducted on a 200 mm whole wafer. e. Raman spectrum map of the intensity ratio of the E12g peak to the Si peak, conducted on a 200 mm whole wafer.

Extended Data Fig. 3 TEM analysis of MOCVD-grown MoS2.

a. Dark-field TEM images of MOCVD-grown MoS2 obtained from varios angles. The image at the top center represents the corresponding diffraction pattern. b. Grain mapping image obtained by SADP (Selected area diffraction pattern) images. The grain size is estimated in range from 50 nm to 100 nm. c. HAADF-STEM (High-angle annular-dark-field scanning tunneling electron microscopy) images showing two grains with a grain boundary. d. Higher magnification and Gaussian-processed view of c. The red spheres represent Mo atoms, while the yellow spheres represent S atoms. It particularly demonstrates a S-deficient environment compared to Mo at the grain boundary.

Extended Data Fig. 4 XPS analysis of MoS2 samples with varying crystallinity.

a. XPS spectra of three MoS2 samples with different crystallinity. The top spectrum represents MoS2 single crystal, the middle one corresponds to polycrystalline MoS2 grown with a grain size of 500 nm, and the bottom spectrum is for polycrystalline MoS2 used in this study with a grain size of less than 100 nm. While the MoS2 single crystal exhibits minimal presence of Mo 6+ or 3+ peaks, the other two MoS2 samples show observable peaks for both Mo 6+ and 3+ states. Here, the intensity of the 6+ peak indicates the extent of oxidation to MoO3, while the size of the 3+ peak is directly related to the sulfur vacancy concentration. b. The Mo:S ratio and sulfur vacancy concentration extracted from the XPS spectra for each sample. Here, the Mo:S ratio has been normalized to the crystal sample. It clearly indicates that the polycrystalline sample indeed has a sulfur-deficient environment. Furthermore, the increase in sulfur vacancy concentration as the grain size decreases, coupled with a decrease in the Mo:S ratio, indirectly suggests that sulfur vacancies are generated at grain boundaries.

Supplementary information

Supplementary Information

Supplementary Sections 1–8, Figs. 1–19 and References.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kwon, J., Seol, M., Yoo, J. et al. 200-mm-wafer-scale integration of polycrystalline molybdenum disulfide transistors. Nat Electron 7, 356–364 (2024). https://doi.org/10.1038/s41928-024-01158-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-024-01158-4